The power of memory. Secured.

# I<sup>2</sup>C Interface Specification

223-0017-005 REV E 3/14

## Table of contents

| Notices and other considerations           | 2  |

|--------------------------------------------|----|

| Introduction                               |    |

| Functional description                     | 5  |

| Operating features                         | 7  |

| Instructions                               | 11 |

| Read operation                             | 14 |

| Panel/board-mount receptacle descriptions  |    |

| Electrical interface                       |    |

| Timing diagrams                            |    |

| Electrostatic discharge (ESD)              |    |

| Memory device power and signal control     |    |

| I <sup>2</sup> C read and write procedures |    |

| Addendum                                   |    |

| IIK & IIT device interfacing               |    |

| Acknowledgement                            | 41 |

| Revision History                           |    |

| -                                          |    |

The power of memory. Secured.

1

## Notices and other considerations

|                         | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Important<br>notices    | <ul> <li>Datakey guarantees the quality of its devices by testing each device before shipment. However, installing and using Datakey products is the responsibility of the purchaser and is in no way guaranteed by Datakey</li> <li>Timing data, electrical characteristics, and signal descriptions are based on a compilation of several approved manufacturers' specifications. Datakey reviews the specifications of all approved vendors, and then "de-rates" the specifications as needed to ensure that all devices meet our published specifications to ensure that all devices operate correctly within an application. Designing to a particular vendor's specifications is not recommended.</li> </ul> |

|                         | • <b>Design Recommendation:</b> It is recommended that all new key/token implementations be designed to operate with power supplies in the range of 2.7 to 3.6 volts. Although there is no immediate or certain future difficulties in the procurement of memory devices that operate with $V_{cc}$ in the 4.5 to 5.5 volt range, it is possible the future availability of such memories may be impacted as semiconductor manufacturers continue to shrink their die geometries. Please contact the factory if you have any questions pertaining to this with your current or legacy design.                                                                                                                      |

|                         | <ul> <li>While the information in this specification has been carefully reviewed, Datakey assumes no liability for any errors or omissions in this specification. Additionally, Datakey reserves the right to make changes to any part of the information in this specification or the products described herein without further notice.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

|                         | • No part of this specification may be photocopied, reproduced, or translated to another language without the written consent of Datakey.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Other<br>considerations | <ul> <li>Although portable key/tokens are designed to withstand harsh environments, many of the conditions that prevent them from working properly in such environments are best addressed through properly designed system interface circuits.</li> <li>Datakey tests all keys/tokens during the manufacturing process. In some cases after the test, data written to a key/token remain. Users should not rely on this</li> </ul>                                                                                                                                                                                                                                                                                |

|                         | data as a means of identifying keys/tokens.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

The power of memory. Secured.

**Datakey**.

## Introduction

| General<br>description                     | Datakey portable memory keys/tokens contain electrically erasable programmable memory (EEPROM) accessed through a serial bus interface, using the Microwire, I <sup>2</sup> C, or SPI bus protocol. Each protocol controls input and output pins of the device through separate serial interface formats.                                                                                                                                                                                                                                            |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Portable<br>memory device<br>uses          | <ul> <li>Portable memory devices add functional versatility to many applications. They personalize equipment operations and transfer data in the following applications:</li> <li>Access control devices</li> <li>Instrument calibration equipment</li> <li>Fuel dispensers</li> <li>Medical treatment systems</li> </ul>                                                                                                                                                                                                                            |

| Memory device<br>design criteria           | <ul> <li>Portable memory applications require memory devices that can survive outside traditional environments, while maintaining data integrity when inserted and removed from the hosts powering them. Therefore, all portable memory devices must comply with the following basic design criteria:</li> <li>Resist dirt and other contaminates</li> <li>Transfer data reliably</li> <li>Tolerate electrostatic discharge</li> <li>Retain data when power is removed</li> <li>Retain data when exposed to certain environmental hazards</li> </ul> |

| Manufacturers'<br>design<br>responsibility | <ul> <li>Portable memory device manufacturers must address the above basic design criteria because they must develop memory devices capable of surviving in harsh environments. When a memory device is integrated into a larger system, the following design considerations become important:</li> <li>How to dissipate electrostatic discharge (ESD)</li> <li>How to maintain device data integrity</li> <li>How to prevent host system disruptions when inserting and removing a key/token</li> </ul>                                             |

Continued on next page

#### Introduction, continued

| Portable<br>memory devices<br>from Datakey | Datakey designs and manufactures portable, rugged keys/tokens containing non-<br>volatile memory. Since 1976 our tough, reliable, and<br>re-programmable keys, tokens, receptacles, and systems have solved data<br>transport and access control problems in the most extreme environments. |  |  |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                            | Our I <sup>2</sup> C keys/tokens contain serial EEPROMs accessed through a simple "two-wire" serial interface. Simple instructions control data transfers to and from the I <sup>2</sup> C memory. This interface specification describes those instructions.                               |  |  |  |

|                                            | Integrity is ensured by methods described in this specification.                                                                                                                                                                                                                            |  |  |  |

| Contents of the specification              | The remaining pages in this specification discuss $I^2C$ design criteria for portable-<br>memory devices along with how to handle these devices in typical applications.                                                                                                                    |  |  |  |

|                                            |                                                                                                                                                                                                                                                                                             |  |  |  |

## **Functional description**

**Keys/Tokens**

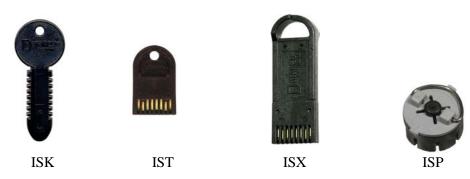

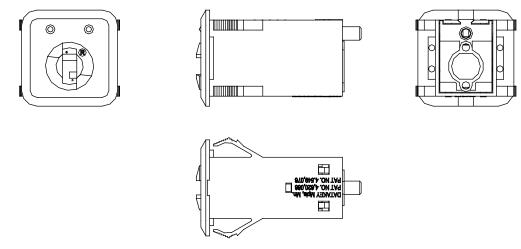

Figure 1 shows examples of serial EEPROM devices available from Datakey. Each type of key/token easily mates to a custom receptacle, which provides access to  $I^2C$  communication, power, and ground signals.

**Signals** Communication between the microcontroller and devices on an I<sup>2</sup>C bus uses two signals:

- Serial Clock (SCL)

- Serial Data/Address (SDA)

These signals, along with the SIZE,  $V_{CC}$  (*supply voltage*) and ground signals are present on all keys/tokens.

Table 1 presents KC4210 and SR4210 receptacles signal/pin acronyms and descriptions.

#### Table 1: KC4210 and SR4210 Signals Acronyms and Descriptions

| Signal Acronym  | Signal Description     |

|-----------------|------------------------|

| SIZE            | Size (Addressing mode) |

| SDA             | Serial Data/Address    |

| SCL             | Serial Clock           |

| V <sub>CC</sub> | Supply Voltage         |

| V <sub>SS</sub> | Ground                 |

Continued on next page

The power of memory. Secured

#### Functional description, continued

| SIZE pin                             | The SIZE pin indicates if a key/token is greater than 16 kilobits in size.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | • The SIZE pin on keys/tokens, 16 kbits or less in size is open (not connected).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                      | • The SIZE pin on keys/tokens greater than 16 kbits is internally connected to ground. The host application can use a simple hardware detection circuit to read the SIZE pin and adjust the addressing protocol.                                                                                                                                                                                                                                                                                                  |

|                                      | • Keys/tokens with memory sizes greater than 16 kbits require two address bytes following the control byte in an I <sup>2</sup> C transaction.                                                                                                                                                                                                                                                                                                                                                                    |

|                                      | • Keys/tokens with memory sizes less than or equal to 16 kbits only require one address byte following the control byte. Bits in the control byte are used as the most significant bits of a memory location.                                                                                                                                                                                                                                                                                                     |

|                                      | For more information about addressing, see the Operating Features and the<br>Instructions sections of this specification.                                                                                                                                                                                                                                                                                                                                                                                         |

| Serial<br>data/address<br>(SDA)      | SDA is a bidirectional signal. It enables data and address information transfers between the master ( <i>host</i> ) and the memory device. Address and data information is valid on the SDA signal when the clock (SCL) signal is high. For normal operation, signal level changes only occur when the SCL signal is low. Signal level changes on the SDA while the SCL is high indicate a start or stop condition. ( <i>See Start/Stop conditions in the Operating Features section of this specification</i> ). |

|                                      | The SDA pin is an open-drain terminal, requiring a pull-up resistor to Vcc for proper operation. Typical values for pull-up resistors are $10k\Omega$ for operation at 100 kHz, and $2k\Omega$ for operation at 400 kHz.                                                                                                                                                                                                                                                                                          |

| Serial clock<br>(SCL)                | The SCL signal synchronizes the communication between the master device and the memory chip. The master or host hardware controls the SCL signal.                                                                                                                                                                                                                                                                                                                                                                 |

| Supply voltage<br>(V <sub>CC</sub> ) | Datakey $I^2C$ keys/tokens will operate throughout a $V_{CC}$ range from 2.7 to 5.5 volts.<br>The supply voltage must be controlled so that keys/tokens are not inserted into live receptacles. See section entitled "Memory device power and signal control."                                                                                                                                                                                                                                                    |

| Ground<br>(Vss)                      | The ground signal and the system ground signal are common.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

WWW.DATAKEY.COM

The power of memory. Secured.

6

## **Operating features**

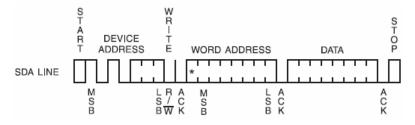

| Master/slave<br>operation | All Datakey $I^2C$ keys/tokens are compatible with the $I^2C$ bus standard. All keys/tokens operate as slave devices on the $I^2C$ bus; they will act as a receiver or transmitter depending on data direction. A master device controls the serial clock (SCL) line.                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

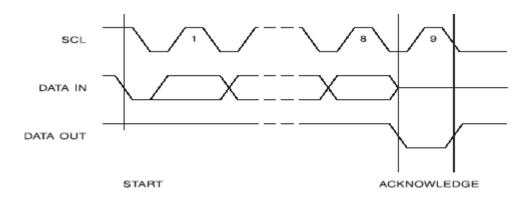

| Bus protocol              | All Datakey I <sup>2</sup> C keys/tokens function as serial EEPROM devices on the I <sup>2</sup> C bus.<br>Data transfers on an I <sup>2</sup> C bus must begin with an idle bus condition ( <i>SCL and SDA lines high</i> ). All I <sup>2</sup> C bus transactions begin with a start condition from the master device. A control byte is the first byte sent by the master following the start condition. The control byte specifies that the bus transaction be for serial EEPROM memory, the device or memory address, and the type of operation ( <i>read or write</i> ). Additional bytes are sent or received, depending on the type of instruction or transaction. |

|                           | The receiving device transmits an acknowledge bit between each byte. It is the responsibility of the master device to generate clock pulses for the acknowledge bit. An $I^2C$ bus transaction ends when a stop condition appears on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                           | Data on the SDA line must be stable when the SCL line is high and can change when<br>the SCL line is low. Any change in the SDA line while the SCL line is high will be<br>interpreted as a start or stop condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Start/stop<br>conditions  | Start Condition: A high-to-low transition of the SDA line while the SCL is high creates a start condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           | Stop Condition: A low-to-high transition of the SDA line while the SCL is high creates a stop condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | Figure 2 shows start and stop condition timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                           | SDA<br>SCL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           | I     I       START     STOP   Figure 2: Start and Stop Condition Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                           | Figure 2. Start and Stop Condition Finning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Continued on next page

WWW.DATAKEY.COM

7

#### Operating features, continued

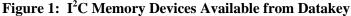

AcknowledgeAll control bytes, addresses, and data transmit to the memory device as 8-bit bytes.bitThe key/token will transmit an acknowledge bit (logic "0") on the ninth clock cycle<br/>to indicate receiving the transmitted byte. Similarly, when transmitting data from the<br/>memory device (reading), the master will provide the logic "0" acknowledge bit on<br/>the ninth clock cycle. In either case, the master device is responsible for generating<br/>the clock signal. Figure 3 shows the acknowledge-bit timing.

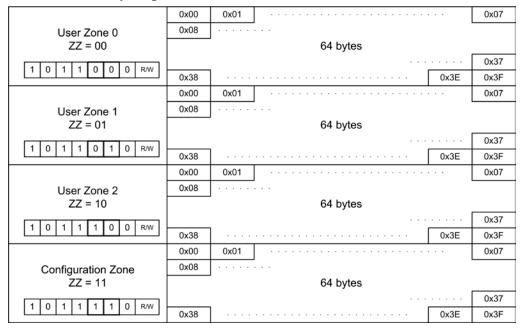

Device addressing The control byte specifies hardware addressing on the I<sup>2</sup>C bus. It is the first byte sent following a start condition. The most significant four bits (*bits* "7" *through* "4") of the control byte are 1, 0, 1, 0, respectively, for all serial EEPROM memory devices that are compatible with the I<sup>2</sup>C bus. Bits "3" through "1" specify the individual device address or internal memory addressing, depending on the size of the key/token. The last bit (*bit* "0") specifies whether the operation is a read (*high*) or write (*low*) transaction.

Continued on next page

WWW.DATAKEY.COM

#### **Operating features,** continued

| Cascading   | Some keys/tokens support cascading of similar EEPROM memory devices on the same $I^2C$ bus. "Cascading" refers to permitting multiple serial EEPROM devices to reside on the same $I^2C$ bus. It requires the memory device to utilize hardwired device addresses.                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Not all keys/tokens from Datakey support cascading. All standard keys/tokens are hardwired for address "0" if cascading is a feature. If cascading is supported, bits "3" through "1" of the control byte specify the address of the individual EEPROM on the bus. Other serial EEPROM devices on the bus must be wired for other addresses. <sup>1</sup> |

|             | In some cases, keys/tokens do not support cascading. Bits "3" through "1" of the control byte can be used to provide the higher address bits of the internal device memory.                                                                                                                                                                               |

|             | Table 2 indicates the availability of cascading for each model of $I^2C$ keys/tokens from Datakey.                                                                                                                                                                                                                                                        |

|             | Note: All standard keys/tokens from Datakey are hardwired to address "0."                                                                                                                                                                                                                                                                                 |

| Page buffer | The page buffer allows multiple-byte writes within one EEPROM write cycle. Page buffer size varies with the total memory size of the key/token. Table 2 shows the page buffer size in bytes for each I <sup>2</sup> C key/token from Datakey.                                                                                                             |

|             | Continued on next page                                                                                                                                                                                                                                                                                                                                    |

<sup>1</sup> Contact Datakey for custom key/token addressing.

WWW.DATAKEY.COM

#### **Operating features, continued**

I<sup>2</sup>C interface<br/>informationTable 2 shows the Key interface information for each I<sup>2</sup>C key/token from Datakey.<br/>For specific information about read and write operations, see the Instructions section<br/>of this specification.

| Key/token | Size (bytes) | Address Range             | Address Bytes | Page Buffer | Cascadable |

|-----------|--------------|---------------------------|---------------|-------------|------------|

| ISK1000   | 128          | 0 ~ 0x7F                  | 1             | 8           | No         |

| IST1000   |              |                           |               |             |            |

| ISK4000   | 512          | 0 ~ 0x1FF                 | 1 + 1 bit     | 16          | No         |

| IST4000   |              |                           |               |             |            |

| ISP4000   |              |                           |               |             |            |

| ISK16000  | 2,048        | 0 ~ 0x7FF                 | 1 + 3 bits    | 16          | No         |

| IST16000  |              |                           |               |             |            |

| ISK64K    | 8,096        | $0 \sim 0 \times 1 FFF$   | 2             | 32          | Yes, 8     |

| IST64K    |              |                           |               |             |            |

| ISK256K   | 32,768       | $0 \sim 0 x7 FFF$         | 2             | 64          | Yes, 4     |

| IST256K   |              |                           |               |             |            |

| ISX512K   | 65,536       | $0 \sim 0x7FFF$ (block 1) | 2             | 64          | No         |

|           |              | $0 \sim 0x7FFF$ (block 2) |               |             |            |

**Table 2: Key Interface Information**

#### Notes:

- The address bytes column specifies the number of address bytes that follow the control byte used to specify the internal address of the memory device. The number of bits used in the control word to specify an internal memory address is relevant to keys or tokens of 16 kilobits or less in size.

- In the Cascadeable column, the numbers represent the EEPROM devices that may reside on the bus.

- The ISX512K is addressed as two 32K-byte blocks. Bit position "1" of the control byte specifies which 32K block is being addressed.

- It is recommended that all new key/token implementations not rely on specified page size for achieving a wrap-around effect for the effective memory address. Although Datakey has no intention to deviate from the listed specification, some semiconductor manufacturers offer devices with page sizes that differ from those published here. We feel a good engineering practice would be to not rely on the listed value in the event availability becomes an issue in the future. The page size in our memory products will be at least as large as what is specified here.

WWW.DATAKEY.COM

Datakey.

### Instructions

#### Byte write

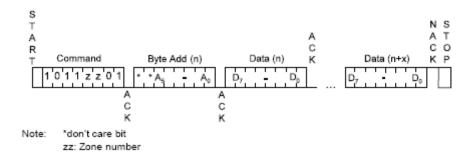

Following the start condition from the master device, the memory device receives a control byte. The control byte consists of the following bits:

- Device code (1 0 1 0 for all serial EEPROM products)

- Device or memory address (depending on product)

- R/W bit (*logic-level "0" for a write operation*)

The control byte configuration is as follows:

| 1 | 0 | 1 | 0 | P2 | P1 | P0 | R/W |

|---|---|---|---|----|----|----|-----|

|---|---|---|---|----|----|----|-----|

**Note:** The ISX512K Token is organized as two separate 32k-byte blocks. P0 of the control byte specifies which 32K block is being addressed. This applies to all ISX512K transactions.

The acknowledge bit is transmitted by the key/token on the ninth clock cycle. Depending on memory size, one or two address bytes will follow the control byte. An acknowledge bit is sent after each 8-bit transmission. The data byte for the addressed memory location is transmitted following the address. The master device must terminate the write sequence by generating a stop condition. This will start an internal write cycle to the non-volatile memory. During an internal write cycle, the key/token will not respond to any commands and will not issue an acknowledge bit.

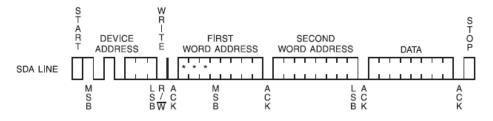

Figures 4 and 5 show one- and two-byte address write operation timing for one- and two-byte addressing keys/tokens.

Figure 5: Two-Byte Address, Single-Byte Write Operation Timing

Continued on next page

WWW.DATAKEY.COM

#### Instructions, continued

Page writeA page write and a byte write start in a similar manner. However, with page writes<br/>instead of generating a stop condition after the first data byte, the host can transmit<br/>additional bytes up to the size of the page buffer for the key/token. The size of the<br/>page buffer depends on key/token memory size (see Table 2). The key/token<br/>transmits an acknowledge bit after each data byte. A stop condition terminates the<br/>write sequence, and initiates the internal write cycle. Again, the key/token will not<br/>issue acknowledge bits during the internal write cycle.

The page buffer operates on address boundaries equal to the size of the buffer. For example, a 32-byte page buffer will only increment the lower five address bits automatically when writing to the buffer. Data written beyond the upper limit of the page boundary will rollover and is stored at the beginning address of the page buffer. Similarly, if the data bytes written to the page exceed the page buffer size, the previous data will be overwritten.

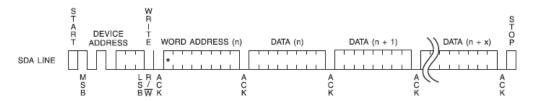

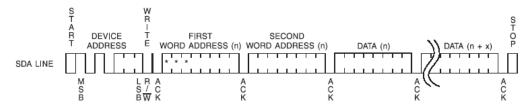

Figures 6 and 7 show one- and two-byte address page-write operation timing for oneand two-byte addressing keys/tokens.

Figure 6: One-Byte Address, Page-Write Operation Timing

Figure 7: Two-Byte Address, Page-Write Operation Timing

The power of memory. Secured

Continued on next page

#### Instructions, continued

| Acknowledge<br>polling | Acknowledge polling can determine when the internal-write cycle of the EEPROM is complete. Immediately after the stop condition terminates the byte or page-write operation, a write cycle starts automatically. During the write cycle, the memory device will not respond with a zero-level acknowledge bit.                                           |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | To test for write-cycle completion, the master will issue a start condition and control<br>byte, and then look for the acknowledge bit from the key/token. If the write cycle is<br>complete, the memory will respond with a zero-level acknowledge bit. If the write<br>cycle is in process, a high-level signal will be read on the ninth clock cycle. |

## **Read operation**

**Read cycles**

Write and read operations initiate in much the same manner. The only difference is the read/write bit in the control byte is set to "1."

There are three basic read operations:

- Current-address read

- Random read

- Sequential Read

Currentaddress read operation

Provided power has not been removed from the key/token, an internal address counter is maintained that points to the memory location following the last address accessed during a read or write operation. The address pointer rolls over to the beginning of memory if the last address accessed was the last address in the memory range.

The current address can be read by issuing a start condition followed by the control byte with the read/write bit set to "1." The memory device will issue an acknowledge bit on the ninth clock cycle and output the data at the current address on subsequent clock cycles. The master terminates the current address read operation by issuing a "no acknowledge" bit "1" followed by a stop condition. The current-address read operation is the same for single and two-byte addressing keys/tokens.

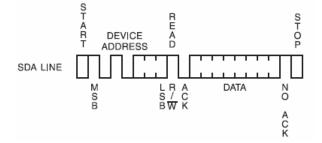

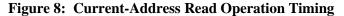

Figure 8 shows current-address read operation timing.

Continued on next page

The power of memory. Secured

#### Read operation, continued

Random-

operation

A random-address read operation requires the internal address pointer to be set with address read the desired memory location address. This is done by sending the address as part of a write operation. Following a start condition the control byte-including any extended address bits—is sent with the read/write bit set to "0" for a write operation. The memory device will respond with an acknowledge bit. The master device will send the one- or two-byte address.

> Once the address is clocked into the device, the master will issue another start condition. The control byte is sent again with the read/write bit set to "1." The data at the address location will be clocked out following the acknowledge bit. An acknowledge bit will be issued by the memory device following each 8-bit address byte. The master terminates the random address read operation by issuing a "no acknowledge" bit "1" followed by a stop condition.

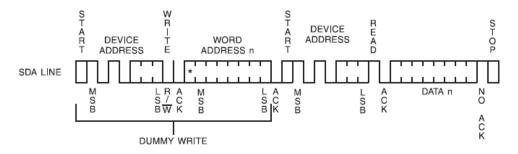

Figures 9 and 10 show the random-address read operation timing for one- and twobyte addressing keys/tokens.

Figure 9: One-Byte Address, Random-Address Read Operation Timing

Figure 10: Two-Byte Address, Random-Address Read Operation Timing

*Continued on next page*

#### Read operation, continued

| Sequential read<br>operation | A sequential-read operation reads the entire memory contents with one instruction.<br>The sequential read operation is initiated in the same manner as the random read or<br>current-address read operation. Instead of responding with a no-acknowledge bit<br>followed by a stop condition, the master will issue an acknowledge bit. |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | The internal address pointer will automatically increment and the data from the next location will clock out. The master can terminate the sequential-read operation after any byte read by sending a no-acknowledge bit followed by a stop condition.                                                                                  |

|                              | Figure 11 shows the sequential-read operation, following the dummy-write operation timing.                                                                                                                                                                                                                                              |

|                              | DEVICE ADDRESS D C C C C C P<br>SDA LINE                                                                                                                                                                                                                                                                                                |

Figure 11: Sequential-Read Operation Timing

| Panel/board-mount rec | eptacle descr | iptions |

|-----------------------|---------------|---------|

|-----------------------|---------------|---------|

| Receptacles                          | The receptacles are used to interface the host system directly with specific serial data keys/tokens. The types are the KC4210, KC4210PCB, SR4210, and the SR4210PCB.                                                                                                                                                                                                                                                                                       |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | A Last On/First Off (LOFO) switch in the key/token receptacle enables the host system to determine when a key/token is present. Upon insertion of a key/token, the LOFO contact connects to ground. Conversely, when the key is removed, the LOFO contact is open. The LOFO contact allows system designers to detect the presence of a key/token, and protects the host bus by applying power only when a key/token is fully inserted into the receptacle. |

| KC4210 panel-<br>mount<br>receptacle | The KC4210 panel-mount design is for applications that require easy mounting in a front-panel configuration. To mount the receptacle, simply cut a one-inch square hole in the desired panel location and then snap the receptacle into place. Use a standard 10-pin connector cable ( $5 \times 2$ ) to connect the device to the host. Figure 12 is a picture of the receptacle.                                                                          |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Figure 12: KC4210 Panel-Mount Receptacle

**Note:** It is recommended that the total length of signal conductors, PC board traces, and ribbon cables not exceed eight inches.

Continued on next page

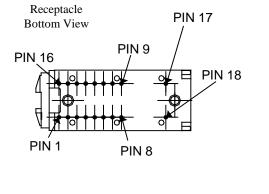

KC4210Figure 13 shows the KC4210 panel-mount receptacle. Refer to spec sheet for<br/>dimensions.drawingGrade in the state of the state

Figure 13: KC4210 Panel-Mount Receptacle Orthographic Drawing

Continued on next page

**KC4210 pin** Figure 14 shows a KC4210 receptacle diagram and a description of its pin outs.

| I <sup>2</sup> C |                           |  |  |

|------------------|---------------------------|--|--|

| Pin No.          | Description               |  |  |

| Pin 1            | NC                        |  |  |

| Pin 2            | Power (V <sub>CC</sub> )  |  |  |

| Pin 3            | Ground (V <sub>SS</sub> ) |  |  |

| Pin 4            | Size                      |  |  |

| Pin 5            | NC                        |  |  |

| Pin 6            | NC                        |  |  |

| Pin 7            | Serial Clock (SCL)        |  |  |

| Pin 8            | Serial Data/Address (SDA) |  |  |

| Pin 9            | NC                        |  |  |

| Pin 10           | LOFO                      |  |  |

Figure 14: KC4210 Receptacle and Pin Outs

Continued on next page

KC4210PCB -<br/>mountThe KC4210PCB-mount receptacle design is for applications where the designer<br/>wants to mount the device directly onto a printed circuit board (PCB). In such<br/>applications, connect the PCB-mount receptacle to the host by soldering its leads<br/>onto a PCB. Figure 15 shows a picture of the receptacle.

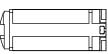

KC4210PCBFigure 16 shows the KC4210PCB-mount receptacle. Refer to spec sheet for<br/>dimensions.drawingGrand and a state of the state o

| <u>- 1411111</u> | - JO |

|------------------|------|

Ч

Figure 16: KC4210PCB-Mount Receptacle Orthographic Drawing

Continued on next page

WWW.DATAKEY.COM

# **KC4210PCB** Figure 17 shows a receptacle diagram and a description of its pin outs.

| I <sup>2</sup> C    |                           |  |  |  |

|---------------------|---------------------------|--|--|--|

| Pin No. Description |                           |  |  |  |

| Pin 1               | Size                      |  |  |  |

| Pin 2               | Ground (V <sub>SS</sub> ) |  |  |  |

| Pin 3               | Power (V <sub>CC</sub> )  |  |  |  |

| Pin 4               | NC                        |  |  |  |

| Pin 5               | Serial Data/Address (SDA) |  |  |  |

| Pin 6               | NC                        |  |  |  |

| Pin 7               | Serial Clock (SCL)        |  |  |  |

| Pin 8               | NC                        |  |  |  |

| Pin 9               | NC                        |  |  |  |

| Pin 10              | Serial Clock (SCL)        |  |  |  |

| Pin 11              | NC                        |  |  |  |

| Pin 12              | Serial Data/Address (SDA) |  |  |  |

| Pin 13              | NC                        |  |  |  |

| Pin 14              | Power (V <sub>CC</sub> )  |  |  |  |

| Pin 15              | Ground (V <sub>SS</sub> ) |  |  |  |

| Pin 16              | Size                      |  |  |  |

| Pin 17              | LOFO                      |  |  |  |

| Pin 18              | LOFO                      |  |  |  |

#### Figure 17: KC4210PCB Receptacle and Pin Outs

KC4210 keyThe KC4210 panel- and board-mount receptacles accept the ISK style key, shown instyleFigure 18.

Figure 18: ISK Key for the KC4210 Receptacle

Continued on next page

WWW.DATAKEY.COM

The power of memory. Secured.

21

SR4210 panel-The SR4210 panel-mount version is designed for applications that require easy mount mounting in a front-panel configuration. To mount the SR4210 panel-mount receptacle receptacle, simply cut a hole based on the dimensions shown on the SR4210 spec sheet in the desired panel location and then slip it into place. A standard 10-pin connector cable  $(5 \times 2)$  is used to connect the device to the host. A Last On/First Off (LOFO) switch in the receptacle enables the host system to determine when a token is present.

Figure 19: SR4210 Panel-Mount Receptacle and Clip

**Note:** It is recommended that the total length of signal conductors, PC board traces, and ribbon cables not exceed eight inches.

SR4210 Figure 20 shows the SR4210 panel-mount receptacle. Refer to spec sheet for dimensions. orthographic

drawing

Continued on next page

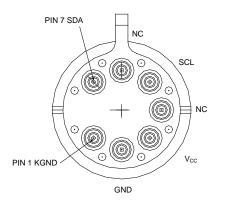

**SR4210 pin** Figure 21 shows a receptacle diagram and a description of its pin outs.

| I <sup>2</sup> C |                           |  |  |

|------------------|---------------------------|--|--|

| Pin              | Description               |  |  |

| Pin 1            | NC                        |  |  |

| Pin 2            | Power (V <sub>CC</sub> )  |  |  |

| Pin 3            | Ground (V <sub>SS</sub> ) |  |  |

| Pin 4            | Size                      |  |  |

| Pin 5            | NC                        |  |  |

| Pin 6            | NC                        |  |  |

| Pin 7            | Serial Clock (SCL)        |  |  |

| Pin 8            | Serial Data/Address (SDA) |  |  |

| Pin 9            | NC                        |  |  |

| Pin 10           | LOFO                      |  |  |

#### Figure 21: SR4210 Receptacle and Token Diagrams and Pin Outs

SR42XXPCBThe information on the SR4210PCB below also applies to the SR4220, SR4230mountboard-mount receptacles. Dimensions can be found in the corresponding specreceptaclessheets. Contact the factory for information on SMT options.

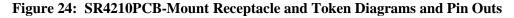

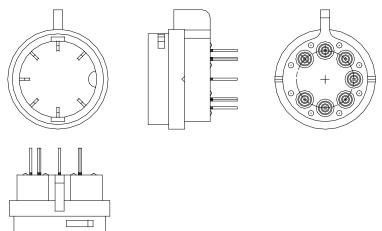

SR4210PCB-<br/>mountThe SR4210PCB-mount receptacle design is for applications where the designer<br/>wants to mount the receptacle directly onto a PCB. In such applications, mount the<br/>receptacle to the host by soldering its leads onto a PCB. Figure 22 shows a picture of<br/>the receptacle.

Figure 22: SR4210PCB-Mount Receptacle

Continued on next page

WWW.DATAKEY.COM

**Datakey**.

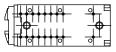

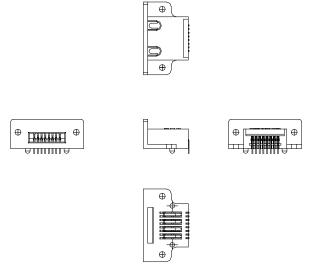

SR4210PCBFigure 23 shows the SR4210PCB board-mount receptacle. Refer to spec sheet for<br/>dimensions.orthographicdimensions.

Figure 23: SR4210PCB-Mount Receptacle Orthographic Drawing

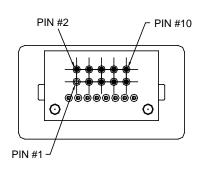

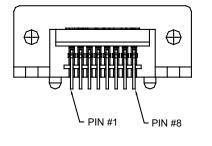

**SR4210PCB** Figure 24 shows a SR4210PCB-mount receptacle and a description of its pin outs.

| I <sup>2</sup> C |                           |  |  |

|------------------|---------------------------|--|--|

| Pin              | Description               |  |  |

| Pin 1            | LOFO                      |  |  |

| Pin 2            | Power (V <sub>CC</sub> )  |  |  |

| Pin 3            | Size                      |  |  |

| Pin 4            | Serial Clock (SCL)        |  |  |

| Pin 5            | NC                        |  |  |

| Pin 6            | Serial Data/Address (SDA) |  |  |

| Pin 7            | Ground (V <sub>SS</sub> ) |  |  |

| Pin 8            | LOFO                      |  |  |

Continued on next page

Slim token styles & pin outs The SR4210 panel- and PCB-mount receptacles accept the IST- and ISX-token style with memory sizes from 1Kb to 512Kb. Figure 25 shows the token styles and pinout. **Note:** the token has redundant contacts, therefore the pinout shown applies to both views of the token.

Figure 25: IST Token and ISX Extended Token Styles for the SR4210 Receptacle and Pin Outs

**KSD receptacle** The KSD receptacle accepts ISP plugs. It can be used in board- and panel-mount applications. Figure 26 and 27 show pictures of the KSD receptacle and ISP plug.

Figure 26: KSD Receptacle

Figure 27: ISP Plug

Continued on next page

WWW.DATAKEY.COM

KSD receptacle orthographic drawing

Figure 28 shows the KSD board-mount receptacle. Refer to spec sheet for dimensions.

Figure 28: KSD Receptacle Orthographic Drawing

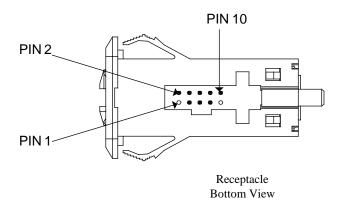

KSD/ISP pinFigure 29 shows a bottom view of a KSD receptacle diagram and a description of its<br/>pin outs when used with an ISP plug.

| I <sup>2</sup> C |                           |  |  |  |

|------------------|---------------------------|--|--|--|

| Pin              | Pin Description           |  |  |  |

| Pin 1            | KGND*                     |  |  |  |

| Pin 2            | Ground                    |  |  |  |

| Pin 3            | Power (VCC)               |  |  |  |

| Pin 4            | NC                        |  |  |  |

| Pin 5            | Serial Clock (SCL)        |  |  |  |

| Pin 6            | NC                        |  |  |  |

| Pin 7            | Serial Data/Address (SDA) |  |  |  |

\*Note: KGND is connected to GND inside the plug. When a plug is inserted into the receptacle, KGND is pulled "low". The host monitors the KGND signal to determine the presence of the Plug..

#### Figure 29: KSD/ISP Receptacle Pin-Out Positions and Description

WWW.DATAKEY.COM

## **Electrical interface**

Electrical characteristics

Table 3 shows absolute maximum values and temperatures for serial  $I^2C$  keys/tokens; Tables 4 and 5 show DC and AC characteristics for  $I^2C$  keys/tokens.

# Caution

The conditions shown in Table 3 are stress ratings only. Stressing  $I^2C$  keys/tokens beyond the limits specified in Tables 4 and 5 could compromise performance or cause permanent damage to keys or tokens.

| Symbols             | Parameters             | Min/Max     | Units |

|---------------------|------------------------|-------------|-------|

| V <sub>CC</sub>     | Supply voltage         | 6.25        | V     |

| V <sub>IN/OUT</sub> | All pins w.r.t. Ground | -0.5 to 6.5 | V     |

| T <sub>STG</sub>    | Storage temperature    | -65 to 150  | °C    |

| T <sub>BIAS</sub>   | Operating temperature  | -40 to 85   | °C    |

Notes:

Keys/tokens manufactured before 2004 have an operating temperature range of 0 to 70°C.

**Design Recommendation:** It is recommended that all new key/token implementations be designed to operate with power supplies in the range of 2.7 to 3.6 volts. Although there is no immediate or certain future difficulties in the procurement of memory devices that operate with  $V_{cc}$  in the 4.5 to 5.5 volt range, it is possible the future availability of such memories may be impacted as semiconductor manufacturers continue to shrink their die geometries. Please contact the factory if you have any questions pertaining to this with your current or legacy design.

Continued on next page

#### Electrical interface, continued

| Table 4: | <b>DC Electrical</b> | Characteristics |

|----------|----------------------|-----------------|

|----------|----------------------|-----------------|

| Symbols               | Parameters               | Min     | Max       | Units | Conditions                                                 |

|-----------------------|--------------------------|---------|-----------|-------|------------------------------------------------------------|

| V <sub>CC</sub>       | Supply voltage           | 2.7     | 5.5       | V     |                                                            |

| V <sub>IH</sub>       | High-level voltage input | 0.7xVcc | Vcc + 0.5 | V     |                                                            |

| V <sub>IL</sub>       | Low-level voltage input  | -0.6    | 0.3xVcc   | V     |                                                            |

| V <sub>OL</sub>       | Low-level voltage output |         | 0.4       | V     | $I_{OL} = 2.1 \text{ mA}, V_{CC} = 2.5 \text{ V}$          |

| I <sub>LI</sub>       | Input-leakage current    |         | ± 10.0    | μA    | $V_{IN} = 0.1 V$ to $V_{CC}$                               |

| I <sub>LO</sub>       | Output-leakage current   |         | ± 10.0    | μA    | $V_{OUT} = 0.1 V$ to $V_{CC}$                              |

| C <sub>IN</sub>       | Input-pin capacitance    |         | 10.0      | pF    | $V_{CC} = 5.0, T_a = 25^{\circ}C, F_{SCL} = 1 \text{ MHz}$ |

| C <sub>OUT</sub>      | Output-pin capacitance   |         | 10.0      |       | $V_{CC} = 5.0, T_a = 25^{\circ}C, F_{SCL} = 1 \text{ MHz}$ |

| I <sub>CC read</sub>  | Supply-current, read     |         | 2.0       | mA    | $V_{CC} = 5.5$ , SCL = 400 kHz                             |

| I <sub>CC write</sub> | Supply-current, write    |         | 5.0       | mA    | $V_{CC} = 5.5$ , SCL = 400 kHz                             |

| I <sub>CCS</sub>      | Supply-current standby   |         | 6.0       | μA    | $SDA = SCL = V_{CC}$                                       |

Continued on next page

WWW.DATAKEY.COM

#### Electrical interface, continued

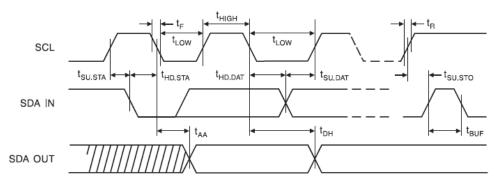

| Symbols             | Parameters                          | Min  | Max | Units |

|---------------------|-------------------------------------|------|-----|-------|

| F <sub>SCL</sub>    | Clock Frequency                     |      | 400 | kHz   |

| t <sub>HIGH</sub>   | Clock High time                     | 600  |     | ns    |

| t <sub>LOW</sub>    | Clock Low time                      | 1300 |     | ns    |

| t <sub>R</sub>      | SDA and SCL Rise time               |      | 300 | ns    |

| t <sub>F</sub>      | SDA and SCL Fall time               |      | 300 | ns    |

| t <sub>HD:STA</sub> | Start Condition Hold time           | 600  |     | ns    |

| t <sub>SU:STA</sub> | Start Condition Setup time          | 600  |     | ns    |

| t <sub>HD:DAT</sub> | Data Input Hold time                | 0    |     | ns    |

| t <sub>SU:DAT</sub> | Data Input Setup time               | 100  |     | ns    |

| t <sub>SU:STO</sub> | Stop Condition Setup time           | 600  |     | ns    |

| t <sub>AA</sub>     | SCL Low to valid SDA out            |      | 900 | ns    |

| t <sub>DH</sub>     | Data out Hold time                  | 50   |     | ns    |

| t <sub>BUF</sub>    | Bus Free time between transmissions | 1300 |     | ns    |

| TI                  | Noise Suppression time              |      | 50  | ns    |

| t <sub>WC</sub>     | Write Cycle time (byte or page)     |      | 10  | ms    |

| t <sub>PUR</sub>    | Power up to read operation time     |      | 1   | ms    |

| t <sub>PUW</sub>    | Power up to write operation time    |      | 1   | ms    |

**Table 5: AC Electrical Characteristics**

## **Timing diagrams**

$I^2C$  Bus Timing Figure 30 shows the timing for a microcontroller and devices on an  $I^2C$  bus.

Figure 30: I<sup>2</sup>C Bus Timing

30

WWW.DATAKEY.COM

**Datakey**.

The power of memory. Secured.

## **Electrostatic discharge (ESD)**

| Circuit<br>component<br>damage             | A buildup of electrostatic charge gradients across the surface of a memory device<br>can produce voltages that could damage circuit components. To prevent such<br>damage, Datakey portable memory devices integrate materials, circuits, and<br>mechanical barriers that help to ensure uniform voltage across the circuit.                                                                                                                                                                                                                                           |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic-<br>charge voltage<br>levels | Any system that uses memory devices must also provide a means of dissipating electrostatic charges. By simply holding a portable memory device in your hand, it is possible to build up an electrostatic charge across the surface of the memory device, up to 20KV relative to ground. This would be equivalent to connecting a circuit of several hundred picofarads of capacitance with a low-series resistance to the memory device.                                                                                                                               |

| Electrostatic-<br>charge<br>dissipation    | When inserting a portable memory device into a system that is grounded or at some<br>other potential, the built-up charge from handling the memory device must be safely<br>dissipated. This can be done by providing a path to ground for the charge. The path<br>must be controlled to prevent large currents and high voltages from occurring on the<br>memory device and in the receptacle. This can be done by putting a resistor in the<br>circuit trace for the receptacle, and using over-voltage protection devices to direct the<br>charge to system ground. |

WWW.DATAKEY.COM

## Memory device power and signal control

| Poor contact<br>concerns          | When inserting a portable memory device into a receptacle, there can be poor contact between the memory device and the receptacle. There could be several possible                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| concerns                          | causes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                   | • Dirty contact surfaces: To make enough electrical contact, the contact surfaces must be free of contaminants. This requires that the contacts be cleaned through a wiping action from the portable memory device.                                                                                                                                                                                                                                                                                                   |

|                                   | • The contacts could bounce and require some time to settle. This could result in a series of random make and break conditions on any or all of the contacts.                                                                                                                                                                                                                                                                                                                                                         |

|                                   | • When a memory device is removed from a receptacle, the contacts do not always break evenly or cleanly.                                                                                                                                                                                                                                                                                                                                                                                                              |

| Power concerns                    | When power is applied to a memory device when it is inserted or removed from a                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                   | receptacle, random contact makes and breaks could cause significant problems for<br>the memory device and the receptacle. Because the control and address signals are<br>not controlled during those actions, undesirable logic combinations can occur, such<br>as the following:                                                                                                                                                                                                                                     |

|                                   | • Power and ground connections becoming unstable, causing further unpredictability.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                   | • Fast power switching to a memory device can introduce noise into system power and ground distribution circuits, resulting in electrical damage to the memory device and subsequent data corruption.                                                                                                                                                                                                                                                                                                                 |

| Data-<br>corruption<br>prevention | The integrated circuits used in Datakey keys/tokens are designed to reduce the risk of data corruption during transient conditions. For example, keys/tokens require a Write Enable instruction before storing any data. Write instructions are also not permitted if the supply voltage is less than a prescribed value. As effective as these protection schemes might be, they do not always eliminate the potential problems with noise that can occur when power is applied to a circuit via a bouncing contact. |

|                                   | To avoid these problems, it is important to control the key/token's power and signal connections. This can be done by using detection circuits, which are discussed next.                                                                                                                                                                                                                                                                                                                                             |

|                                   | Continued on next page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Continued on next page

The power of memory. Secured.

#### Memory device power and signal control, continued

| Memory device<br>detection<br>circuit | The memory-device detection circuit detects when a memory device is present.<br>Datakey receptacles use Last On/First Off (LOFO) contacts for this purpose. When<br>inserting a memory device into the receptacle, the LOFO contacts make electrical<br>connection only after all memory device contacts are closed. Similarly, the LOFO<br>contacts break before any other contact is open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transistor<br>switch circuit          | <ul> <li>When a receptacle detects a memory device for a certain minimum time, power can then be applied. This delay can be established by using a simple transistor switch circuit with the following characteristics:</li> <li>The power switch should have a low voltage drop when power is applied to the memory device. This will ensure that the voltage supplied to the key/token is within a safe and acceptable range.</li> <li>The circuit should apply power to any pull-up resistors connected to the key/token to prevent power from being applied unintentionally through the signal lines.</li> <li>The circuit should include a bleeder resistor to ensure that power is removed quickly when the switch is turned OFF.</li> <li>The switch should turn power ON fast enough to avoid causing problems in the key/token, and slow enough so that it does not introduce any significant noise into the system-reset circuit.</li> </ul> |

WWW.DATAKEY.COM

# I<sup>2</sup>C read and write procedures

| Procedures     | Follow the procedures below when using a key/token in a receptacle with a power-<br>switching circuit.                                                                                                                                                |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read procedure | The procedure for reading data from a key/token is less critical than the sequence for writing data to that same key/token because the data are not subject to change. To read the data from a key/token, Datakey recommends the following procedure: |

|                | • Insert the key/token                                                                                                                                                                                                                                |

|                | • Detect the key/token using the LOFO contact                                                                                                                                                                                                         |

|                | • Wait for contacts to settle (verify presence of Key/token)                                                                                                                                                                                          |

|                | • Apply power                                                                                                                                                                                                                                         |

|                | • Wait for power to stabilize                                                                                                                                                                                                                         |

|                | Test contact integrity                                                                                                                                                                                                                                |

|                | Read data                                                                                                                                                                                                                                             |

|                | Remove power                                                                                                                                                                                                                                          |

|                | • Remove the key/token                                                                                                                                                                                                                                |

|                |                                                                                                                                                                                                                                                       |

Continued on next page

WWW.DATAKEY.COM

34

#### I2C read and write procedures, continued

| Write<br>procedure               | The write procedure must verify that the key/token is present throughout the write cycle, which will ensure that data is written to the key/token correctly. To write data to a key/token, Datakey recommends the following procedure:                                                                                                |  |  |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                  | • Insert the key/token                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                                  | • Detect the key/token using the LOFO contact                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                  | • Wait for contacts to settle (verify presence of Key/token)                                                                                                                                                                                                                                                                          |  |  |  |  |