### The power of memory. Secured.

## SPI FLASH INTERFACE SPECIFICATION

223-0017-006 REV P 8/23

# SPI Flash Interface Specification

#### Table of contents

| Table of contents                              | 1  |

|------------------------------------------------|----|

| Notices and other considerations               | 2  |

| Introduction                                   | 3  |

| Functional description                         |    |

| Operating features                             |    |

| Instructions                                   |    |

| Instruction descriptions                       | 15 |

| Panel- and board-mount receptacle descriptions |    |

| Electrical interface                           |    |

| Timing diagrams                                | 40 |

| Electrostatic discharge (ESD)                  |    |

| Memory device power and signal control         | 43 |

| SPI Flash read and write procedures            | 45 |

| Addendum A (Sizes Greater than 8Mbits)         | 47 |

| Acknowledgement                                | 50 |

| Revision history                               |    |

|                                                |    |

WWW.DATAKEY.COM

The power of memory. Secured.

1

#### Notices and other considerations

| Important<br>notices    | <ul> <li>Datakey guarantees the quality of its portable memory devices by testing them before shipment. However, installing and using Datakey products is the responsibility of the purchaser and is in no way guaranteed by Datakey.</li> <li>Timing data, electrical characteristics, and signal descriptions are based on a compilation of several approved manufacturer specifications. Datakey reviews the specifications of all approved vendors and "de-rates" the specifications as necessary to ensure that all devices meet our published specifications regardless of the vendor used.</li> </ul> |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | • Customers must design to our published specifications to ensure that all devices operate correctly within an application. Designing to a particular vendor's specification is not recommended.                                                                                                                                                                                                                                                                                                                                                                                                             |

|                         | • While the information in this specification has been carefully reviewed, Datakey assumes no liability for any errors or omissions in this specification. Additionally, Datakey reserves the right to make changes to any part of the information in this specification or the products described herein without further notice.                                                                                                                                                                                                                                                                            |

|                         | • No part of this specification may be photocopied, reproduced, or translated to another language without the written consent of Datakey.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Other<br>considerations | • Although portable memory devices are designed to withstand harsh environments, many of the conditions that prevent them from functioning properly in those environments are best addressed through the proper design of system interface circuits.                                                                                                                                                                                                                                                                                                                                                         |

|                         | • Datakey tests all keys and tokens during the manufacturing process. In some cases, data written to a memory device remains after the test. Users should not rely on this data as a means of identifying keys or tokens.                                                                                                                                                                                                                                                                                                                                                                                    |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

2

# SPI Flash Interface Specification

| Introduction                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General<br>description                     | Datakey portable memory keys and tokens contain programmable memory based on EEPROM or Flash technology. Access to these devices is through a serial bus interface, using the Microwire, I <sup>2</sup> C or Serial Peripheral Interface (SPI) bus protocols. Each protocol controls the device input and output pins through separate serial interface formats.                                                                                                                                |

| Portable<br>memory device<br>uses          | <ul> <li>Portable memory devices add functional versatility to many applications. They personalize equipment operations and transfer data in the following applications:</li> <li>Access control devices</li> <li>Instrument calibration equipment</li> <li>Fuel dispensers</li> <li>Medical treatment systems</li> </ul>                                                                                                                                                                       |

| Memory device<br>design criteria           | Portable memory applications need memory devices that can survive outside traditional environments; they must maintain data integrity when you insert and remove them from their active hosts. Therefore, all portable memory devices must be able to meet the following basic design criteria:                                                                                                                                                                                                 |

|                                            | <ul><li>Resist dirt and other contaminants</li><li>Transfer data reliably</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                            | Tolerate electrostatic discharge                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                            | Retain data when power is removed                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                            | • Retain data when exposed to certain environmental hazards                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Manufacturers'<br>design<br>responsibility | <ul> <li>Portable memory device manufacturers need to meet these basic design criteria because the devices must be capable of surviving in harsh environments. When integrating a memory device into a larger system, manufacturers need to consider the following:</li> <li>How to dissipate electrostatic discharge (ESD)</li> <li>How to maintain device data integrity</li> <li>How to prevent host system disruption when inserting and removing the key or token memory device</li> </ul> |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Continued on next page

WWW.DATAKEY.COM

3

#### Introduction, continued

| Datakey<br>portable<br>memory devices | Datakey designs and manufactures portable, rugged keys and tokens containing<br>non-volatile memory. For more than 29 years, our tough, reliable,<br>re-programmable keys, tokens, receptacles, and systems solve data transport and<br>access control problems for the most extreme environments.                    |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | You can access SPI Flash Keys and tokens containing serial Flash memory devices<br>through a simple four-wire serial interface. Simple instructions control data transfers<br>to and from the SPI Flash memory. This interface specification describes those<br>instructions.                                         |

|                                       | SPI Flash Key and token data-integrity enhancements come through several means, including the Write Enable and Write Disable instructions. These instructions enable and disable the ability to overwrite data stored in the device. The correct use of these instructions reduces the potential for data corruption. |

| This<br>specification                 | The remaining pages in this specification discuss SPI Flash design criteria for portable memory devices and recommend ways to handle them in typical applications.                                                                                                                                                    |

4

## SPI Flash Interface Specification

#### **Functional description**

## Keys and tokens

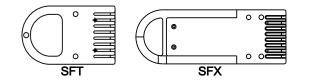

The following are examples of serial Flash devices available from Datakey. Each type of key and token shown below easily mates to a custom receptacle, providing access to its communication, power, and ground signals.

Signals Table 1 shows the signals for the KC4210/KC4210PCB receptacles and the SR4210/SR4210PCB receptacles. Each receptacle is described in the following pages.

Use the KC4210/KC4210PCB receptacles to interface the SFK and SFK5V series keys. Use the SR4210/SR4210PCB receptacles to interface the SFT Tokens and SFX Extended Tokens.

Communication between the microcontroller and devices on an SPI bus uses four signals: an active-low Chip Select (/CS), a Serial Clock (SCK), a Serial Data In (SI) and a Serial Data Out (SO). In addition, an active low-hold (/HOLD) signal suspends communication with the key or token. Those signals, along with the voltage supply ( $V_{CC}$ ) and ground signals, are present on all keys and tokens.

#### **Table 1: Signal Acronyms and Descriptions**

| Signal Acronym  | Signal Description             |

|-----------------|--------------------------------|

| /CS             | Chip Select Input (active-low) |

| SI              | Serial Data Input              |

| SO              | Serial Data Output             |

| SCK             | Serial Clock                   |

| /HOLD           | Hold Input (active- low)       |

| V <sub>CC</sub> | Supply Voltage                 |

| V <sub>SS</sub> | Ground                         |

WWW.DATAKEY.COM

5

The power of memory. Secured

**Datakey**

#### Functional description, continued

| Chip Select<br>(/CS)    | The Chip Select signal is an active-low input to the device. A low level selects the device and places it in the active-power mode. A high level deselects the device and forces standby mode unless an internal programming, erase or write-status register cycle is in progress. After completing the write cycle, the device enters standby mode.                                                                        |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Data In<br>(SI)  | The Serial Data In signal is an input to the device. The instruction, address and data bits serially transfer to the device. Data values latch in on the rising edge of the serial clock signal.                                                                                                                                                                                                                            |

| Serial Data Out<br>(SO) | The Serial Data Out signal is an output from the device. The SO signal and the Serial Clock signal enable synchronous data outputs. Data values shift out on the falling edge of the serial clock signal.                                                                                                                                                                                                                   |

| Serial Clock<br>(SCK)   | The Serial Clock signal is an input to the device. The SCK synchronizes the communication between the master device and the memory chip. The instruction, address, and data bits present on the SI pin clock in on the rising edge of the SCK signal. Data bits on the SO pin shift out on the falling edge of the SCK signal.                                                                                              |

| Supply Voltage<br>(Vcc) | Two versions of SPI Flash Keys and tokens are available based on user-supply voltage requirements. The SFK, SFT, and SFX keys and tokens operate with a 3.3Vdc nominal supply. The SFK5V and SFX5V keys and tokens operate with a 5.0Vdc nominal supply. The Vcc signal must be controlled so that keys and tokens are not inserted into "live" receptacles. See section entitled "Memory Device Power and Signal Control". |

| Ground (Vss)            | The Ground signal and the System Ground signal are common.                                                                                                                                                                                                                                                                                                                                                                  |

# SPI Flash Interface Specification

#### **Operating features**

| Operating<br>features and<br>device capacity | <ul> <li>Datakey SPI Flash memory products share operating features that differ based on the capacity of the memory device. Each device offers features such as the following:</li> <li>Page programming</li> <li>Sector and bulk erasing</li> <li>Ability to monitor programming or erase cycles</li> <li>Ability to write-protect portions of the memory space through software instructions</li> </ul>                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory device<br>addressing                  | You can write data to the addressable memory locations of the memory device by issuing a Write Enable instruction followed by the Page Programming instruction. All SPI Flash memory products are organized in pages of 256 bytes. Programming one byte of data within a 256-byte page achieves the programming of all bytes on that page. Therefore, the Page Programming instruction enables the downloading of up to 256 bytes in the same instruction. That capability reduces the overhead for writing data to the memory device.                                                                                                                                                                                         |

| Sector and chip<br>erase                     | Writing data to the memory device involves changing the state of memory bits from "1" to "0." You cannot program a bit from "0" to "1." SPI Flash memory devices do not include an automatic erase cycle before a write cycle. Therefore, you can erase individual sectors or the entire device with the Sector Erase or Chip Erase instruction. The size of an individual sector and the number of sectors within a device varies with the total capacity of the memory device. Information about the size and number of sectors for each SPI Flash memory type will be discussed later. To reduce the risk of accidentally erasing the memory, a Write Enable instruction must be sent before issuing the Erase instruction. |

|                                              | Continued on next page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Continued on next page

7

#### Operating features, continued

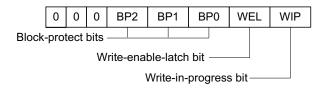

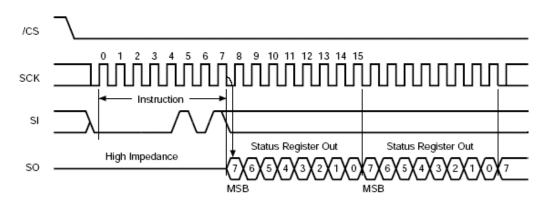

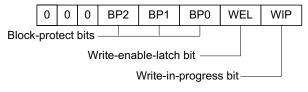

**Status register** The status register contains several status bits. These bits are read or set by specific instructions. Figure 1 shows the status register bit configurations.

<u>The write-in-progress (WIP) bit:</u> The WIP bit shows the status of the programming or erase cycle. When the write or erase cycle is in progress, the WIP bit has a value of "1." After completing the write or erase cycle, the bit will be set to "0."

<u>The write-enable-latch (WEL) bit</u>: The Write Enable or Write Disable instruction sets or resets the WEL bit. Before initiating a write or erase instruction, set the WEL bit, otherwise the instruction will be ignored. When powering up the device, or on the completion of a write or erase cycle, the WEL bit will be automatically reset to "0."

<u>BP2, BP1, and BP0 block-protect bits:</u> The block-protect (BP) bits can be written with the Write Status Register instruction. Setting or resetting the BP bits determines which sectors within the addressable memory space will be write protected. The number of BP bits and memory sectors varies with memory device capacities.

Figure 1: Status Register Bit Configurations

*Continued on next page*

8

#### Operating features, continued

Write<br/>protectionYou can write protect all or part of the addressable memory in all keys and tokens.<br/>The write protected area is based on the value written to the BP bits using the Write<br/>Status Register instruction. Memory locations inside protected sectors become read-<br/>only memory. Table 2 shows the protected sectors for each memory size, and the BP<br/>bit settings.

| Blo | ck-pro  | tect | SFK 1M, SFT 1M    | SFK 2M, SFT 2M    | SFK 4M, SFT 4M    | SFK 8M, SFT 8M    |

|-----|---------|------|-------------------|-------------------|-------------------|-------------------|

| (1  | BP) bit | S    | SFK5V 1M          | SFK5V 2M          | SFK5V 4M          | SFK5V 8M          |

| BP2 | BP1     | BP0  | Protected Sectors | Protected Sectors | Protected Sectors | Protected Sectors |

| 0   | 0       | 0    | None              | None              | None              | None              |

| 0   | 0       | 1    | 3                 | 3                 | 7                 | 15                |

| 0   | 1       | 0    | 2 and 3           | 2 and 3           | 6 and 7           | 14 and 15         |

| 0   | 1       | 1    | All               | All               | 4 to 7            | 12 to 15          |

| 1   | 0       | 0    |                   |                   | All               | 8 to 15           |

| 1   | 0       | 1    |                   |                   | All               | All               |

| 1   | 1       | 0    |                   |                   | All               | All               |

| 1   | 1       | 1    |                   |                   | All               | All               |

**Table 2: Memory Size and Block-Protect Bit Settings**

The 1M and 2M memory sizes do not have a BP2 bit position. This bit-position value should be "0" when data passes with the Write Status Register instruction.

All Page Programming and Erase instructions that affect memory addresses within a protected sector will be ignored.

NOTE: For memory sizes greater than 8Mbits review Addendum A, page 47.

Continued on next page

9

#### Operating features, continued

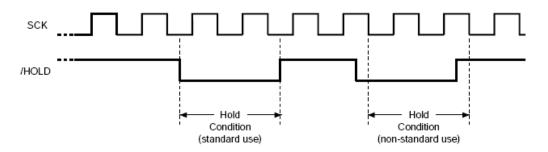

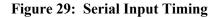

/Hold signal All SPI Flash memory keys and tokens provide access to the /Hold signal. It can interrupt communications with the device without terminating the data output or the instruction. You can use this feature when a higher priority device on the same SPI bus interrupts the controller.

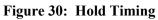

**Hold condition** Normally, a Hold condition starts when the /Hold signal goes low while the Serial Clock (SCK) signal is low. In this case, the Hold condition will start immediately. During a Hold condition, the Serial Data Out (SO) pin will be in a high impedance state, and signals on the SCK and the Serial Data In (SI) pins will be ignored. If the SCK signal is low when the /Hold signal goes high, the Hold condition will end immediately.

If you apply or remove the /Hold signal while the serial clock signal is high, the Hold condition will not start or end until the next falling edge of the SCK signal.

The Hold condition is only effective at suspending communications with the memory device while the device remains selected by the /CS signal. If you deselect the device by removing the low level on the /CS signal during a Hold condition, the internal logic of the device will reset. In this case, reselect the device with a /CS signal. Resend the interrupted instruction once the /Hold signal goes high.

Figure 2 shows standard and non-standard application /Hold signal timing.

Figure 2: Standard and Non-Standard Application /Hold Signal Timing

#### Instructions

Common All Datakey SPI Flash memory products operate with the following set of common instruction set instructions: Basic instructions to read and write from any addressable memory location • Instructions to erase all or a portion of the memory area • Instructions to write-protect areas of memory • Instructions to read the size of the memory device embedded in a key or token • **Device data** All instructions, addresses, and data shift into the device on the Serial Data In (SI) transfers signal. Data shifts out of the device on the Serial Data Out (SO) signal. All serial data shifts in or out, beginning with the most significant bit. Unless you select the device by driving the /CS signal low, serial data on the SI signal will be ignored. Serial data latches into the key or token on the rising edge of the SCK signal. Each instruction sequence begins with an instruction byte followed by an address or data, depending on the instruction. For instructions that require data from the device, such as Read or Read Status instructions, the data shifts out beginning with the most significant bit immediately following the instruction and the data in sequence. Data shifts out on the falling edge of the SCK signal.

Continued on next page

11

#### Instructions, continued

**Instruction set descriptions** Table 3 lists the instruction set common to all SPI Flash keys and tokens. It is possible to follow instruction bits with additional information such as address and data, depending on the type of instruction. Each instruction will be described in detail later.

| Instruction | Description               | Instruction Bits | Address<br>Bytes | Extra<br>Bytes | Data<br>Bytes |

|-------------|---------------------------|------------------|------------------|----------------|---------------|

| WREN        | Write Enable              | 00000110b (06h)  | 0                | 0              | 0             |

| WRDI        | Write Disable             | 00000100b (04h)  | 0                | 0              | 0             |

| RDSR        | Read Status Register      | 00000101b (05h)  | 0                | 0              | 1 - ∞         |

| WRSR        | Write Status Register     | 00000001b (01h)  | 0                | 0              | 1             |

| READ        | Read Data                 | 00000011b (03h)  | 3                | 0              | 1 - ∞         |

| FAST_READ   | Read Data at higher speed | 00001011b (0Bh)  | 3                | 1              | 1 - ∞         |

| PP          | Page Program (write data) | 00000010b (02h)  | 3                | 0              | 1 - 256       |

| SE          | Sector Erase              | 11011000b (D8h)  | 3                | 0              | 0             |

| BE          | Bulk or Chip Erase        | 11000111b (C7h)  | 0                | 0              | 0             |

| DP          | Deep Power-down           | 10111001b (B9h)  | 0                | 0              | 0             |

| RES         | Release from Power-down   | 10101011b (ABh)  | 0                | 3              | 1 - ∞         |

|             | and                       |                  |                  |                |               |

|             | Read Electronic Signature |                  |                  |                |               |

Table 3: Common Instruction Set for SPI Flash Keys and tokens

SPI Flash Key<br/>and token<br/>memory<br/>capacitiesSPI Flash Keys and tokens have different memory capacities based on the device type.SPI Flash Keys and tokens<br/>memory<br/>capacitiesThe addressable memory range is based on the memory capacity. SPI Flash Keys and<br/>tokens are available in memory capacities of 1, 2, 4 or 8 megabits. The memory space<br/>arrangement is byte-wide memory locations organized in 256 byte pages.<br/>Additionally, each device is divided into several sectors of 32,768 bytes or 65,536<br/>bytes, depending on the device type.

Table 4 shows the total device size, the number of pages, the size and address range of each sector, and the number of sectors for each Key and token type.

NOTE: For memory sizes greater than 8Mbits review Addendum A, page 47.

Continued on next page

#### Instructions, continued

| Table 4: Key and Token Capacities and Sector Address Ranges |                              |                              |                              |                              |

|-------------------------------------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|

|                                                             | SFK 1M<br>SFT 1M<br>SFK5V 1M | SFK 2M<br>SFT 2M<br>SFK5V 2M | SFK 4M<br>SFT 4M<br>SFK5V 4M | SFK 8M<br>SFT 8M<br>SFK5V 8M |

| Device Signature                                            | 10h                          | 11h                          | 12h                          | 13h                          |

| <b>Device Size (Bytes)</b>                                  | 131072                       | 262144                       | 524288                       | 1048576                      |

| Pages                                                       | 512                          | 1024                         | 2048                         | 4096                         |

| Page Size (Bytes)                                           | 256                          | 256                          | 256                          | 256                          |

| Sectors                                                     | 4                            | 4                            | 8                            | 16                           |

| Sector Size (Bytes)                                         | 32768                        | 65536                        | 65536                        | 65536                        |

|                                                             |                              |                              |                              |                              |

| Sector Address Rai                                          | nge                          |                              |                              |                              |

| 0                                                           | 00000h to 07FFFh             | 00000h to 0FFFFh             | 00000h to 0FFFFh             | 00000h to 0FFFFh             |

| 1                                                           | 08000h to 0FFFFh             | 10000h to 1FFFFh             | 10000h to 1FFFFh             | 10000h to 1FFFFh             |

| 2                                                           | 10000h to 17FFFh             | 20000h to 2FFFFh             | 20000h to 2FFFFh             | 20000h to 2FFFFh             |

| 3                                                           | 18000h to 1FFFFh             | 30000h to 3FFFFh             | 30000h to 3FFFFh             | 30000h to 3FFFFh             |

| 4                                                           |                              |                              | 40000h to 4FFFFh             | 40000h to 4FFFFh             |

| 5                                                           |                              |                              | 50000h to 5FFFFh             | 50000h to 5FFFFh             |

| 6                                                           |                              |                              | 60000h to 6FFFFh             | 60000h to 6FFFFh             |

| 7                                                           |                              |                              | 70000h to 7FFFFh             | 70000h to 7FFFFh             |

| 8                                                           |                              |                              |                              | 80000h to 8FFFFh             |

| 9                                                           |                              |                              |                              | 90000h to 9FFFFh             |

| 10                                                          |                              |                              |                              | A0000h to AFFFFh             |

| 11                                                          |                              |                              |                              | B0000h to BFFFFh             |

| 12                                                          |                              |                              |                              | C0000h to CFFFFh             |

| 13                                                          |                              |                              |                              | D0000h to DFFFFh             |

| 14                                                          |                              |                              |                              | E0000h to EFFFFh             |

| 15                                                          |                              |                              |                              | F0000h to FFFFFh             |

Table 4: Key and Token Capacities and Sector Address Ranges

Continued on next page

#### Instructions, continued

| Memory<br>addresses                      | You can read data from or write data to any memory location within the address range<br>of the device. Three address bytes or 24 address bits following the Read or Write<br>instruction specify the address location. You can read data beginning with any<br>permissible address. Once data from an address shifts out, the internal address pointer<br>automatically increments, and then you can read data from the next location. In this<br>manner, one Read instruction reads the entire contents of the device. |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | You can write to any address location by specifying the address in the Write<br>instruction. Consecutive locations may be written by sending up to 256 bytes of data.<br>During a write operation, the internal address pointer will increment automatically<br>until it reaches the page boundary. At that point, the address will reset to the<br>beginning of the current page. Therefore, it is possible to overwrite previously written<br>data.                                                                   |

| Sector or<br>Device Erase<br>instruction | SPI Flash memory devices do not have automatic erase cycles while writing data to the memory. Issue a Sector or Bulk Erase instruction before writing data. It is important to note that data is written in pages of 256 bytes, but data is erased as sectors containing 32,768 or 65,536 bytes depending on the memory size.                                                                                                                                                                                           |

|                                          | All Keys and tokens are tested during the manufacturing process. In some cases,                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                          | An Acys and lowens are residu unting the manufacturing process. In some cases,                                                                                                                                                                                                                                                                                                                                                                                                                                          |

All Keys and tokens are tested during the manufacturing process. In some cases, the testing process leaves test data or artifacts on the key or token. Users must erase keys or tokens before using them.

#### Instruction descriptions

Write Enable<br/>instructionIssue a Write Enable (WREN) instruction before each type of write operation,<br/>including the Page Program (PP), Sector Erase (SE), Bulk Erase (BE), and Write<br/>Status Register (WRSR) instructions. The Write Enable instruction sets the write-<br/>enable-latch (WEL) bit in the status register.

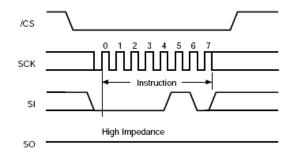

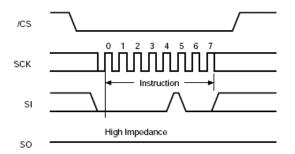

Execute the Write Enable instruction by selecting the device with a low level on the /CS signal—transmitting the instruction on the SI signal and deselecting the device. Figure 3 shows the WREN instruction timing sequence.

Write Disable instruction A Write Disable (WRDI) instruction resets the WEL bit in the status register, which prevents writing or erasing data. Execute the Write Disable instruction by selecting the device with a low level on the /CS signal—transmitting the instruction on the SI signal and deselecting the device. Figure 4 shows the WRDI instruction timing sequence.

Figure 4: WRDI Instruction Timing Sequence

**Note:** The WEL bit will reset automatically when the device powers up or upon the completion of an instruction to program or erase the memory.

Continued on next page

**Datakey**

The power of memory. Secured.

Read Status Register instruction

The Read Status Register (RDSR) instruction reads the contents of the status register. You can read the status register at any time. To determine when a write cycle is complete, read the status register during programming and erase cycles. The value of the write-in-process bit indicates the status of the write cycle.

Execute the RDSR instruction by selecting the device with a low signal on the /CS and transmitting the RDSR instruction on the SI signal. After transmitting the instruction, you can read the status register continuously. This occurs by sending the device a SCK signal. Terminate the RDSR instruction by deselecting the device with a high level on the /CS signal. Figure 5 shows the RDSR instruction timing sequence.

Figure 5: RDSR Instruction Timing Sequence

**Status register** Figure 6 shows the configuration of the status register bits. **bits**

Figure 6: Status Register Bit Configuration

*Continued on next page*

**Datakey** The power of memory. Secured.

16

Status register The number of block-protect (BP) bits is dictated by the memory capacity of the key or bit definitions token. A description of these bits is in the operating features section of this document. The write-enable-latch (WEL) bit is set to "1" with a Write Enable instruction. When the WEL bit is set to "1," the Write or Erase instruction will be effective. The WEL bit will set automatically to "0" when completing any Write or Erase instruction. It will also be set to "0" when the device powers up or when executing a Write Disable instruction. The write-in-progress (WIP) bit shows when the memory is busy with a write or erase operation. When the write or erase cycle is in progress, the bit is set to "1." After completing the write or erase cycle, the bit is set to "0." Write Status The Write Status Register instruction sets the value of the BP bits. All other bits in the Register status register are read-only bits, with the exception of the WEL bit. The WEL bit is (WRSR) set or reset with the WREN and WRDI instructions respectively. instruction Send the Write Enable instruction before the Write Status Register instruction. Execute the Write Status Register instruction by selecting the device with a low level on the /CS signal—transmitting the instruction followed by the data on the SI signal, and deselecting the device. Figure 7 shows the WRSR instruction timing sequence. /CS 10 SCK Instruction Status Register In High Impedance MSB SO Figure 7: The WRSR Instruction Timing Sequence

**Note:** Only the appropriate block protect bits are effective (*bit positions B2, B1, and B0*). See Figure 6. Set all other data bits to a value of "0." The size of the memory device determines the number of BP bits.

Continued on next page

WWW.DATAKEY.COM

The power of memory. Secured.

#### Read Data Bytes (READ) instruction

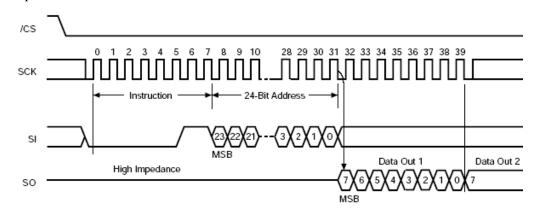

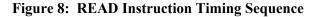

The READ instruction enables reading memory locations within the addressable range of the device. Execute the READ instruction by selecting the device with a low level on the /CS signal—transmitting the instruction on the SI signal, followed by the 24-bit address. The contents of the addressed memory location shift out on the SO signal, on the falling edge of the SCK signal. Figure 8 shows the READ instruction timing sequence.

READ instruction memory addressing

The maximum clock frequency for the READ instruction is specified as  $f_{SCKR}$ . The internal address pointer will increment automatically after outputting a byte of data. Data from the next memory address shifts out on the SO signal as long as there is an SCK signal and the /CS signal remains low. The internal memory address rolls over to location "0" when data from the highest addressable memory location shifts out. To terminate the READ instruction, deselect the device with a high level on the /CS signal.

**Note:** The address bits that reference memory locations beyond the addressable range of the device are ignored.

Continued on next page

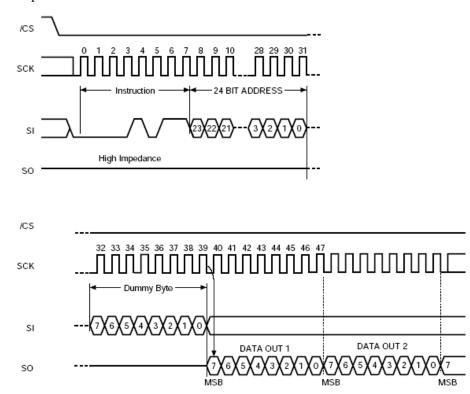

#### Fast Read Data Bytes (FAST\_READ) instruction

The FAST\_READ instruction performs the same function as the Read Data Bytes (READ) the instruction, the 24-bit address, and a dummy byte on the SI signal. The contents of the addressed memory location shift out on the SO signal, on the falling edge of the SCK signal. Figure 9 shows the FAST\_READ instruction timing sequence.

Figure 9: FAST\_READ Instruction Timing Sequences

Continued on next page

WWW.DATAKEY.COM

The power of memory. Secured.

| Fast_Read<br>instruction<br>memory<br>addressing | The maximum clock frequency for the FAST_READ instruction is specified as $f_{SCK}$ .<br>The internal memory address automatically increments after outputting each data byte.<br>Data from the next memory location shifts out on the SO signal as long as there is an SCK signal and the /CS signal remains low. The internal memory address rolls over to location "0" when the data from the highest addressable memory location shifts out.<br>To terminate the FAST_READ instruction, deselect the device with a high level on the /CS signal. |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                  | <b>Note:</b> The address bits that reference memory locations beyond the addressable range of the device are ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

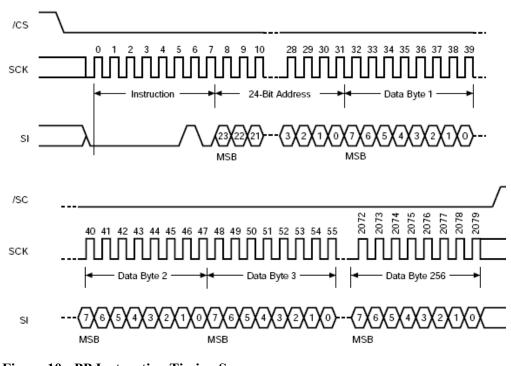

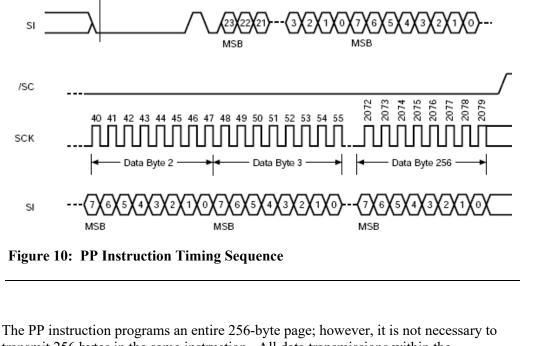

| Programming<br>memory<br>locations               | The Write Data Bytes/Page Program (PP) instruction programs memory locations with data. Erase the memory locations before programming them because the PP instruction can only change bit states from "1" to "0." Before sending a PP instruction, execute a Write Enable (WREN) instruction to set the write-enable-latch bit in the status register.                                                                                                                                                                                               |  |  |

| Page Program<br>(PP) instruction                 | Execute the Page Program instruction by selecting the device with a low level on the /CS signal—transmitting the instruction on the SI signal, followed by the desired 24-bit address and at least one data byte. You can transmit additional data bytes if they reside within the same 256-byte page selection of the address bits.                                                                                                                                                                                                                 |  |  |

|                                                  | To terminate the instruction, deselect the device with a high level on the /CS signal.<br>The /CS signal must go high only after latching the last bit of a data byte to prevent the<br>entire Page Program instruction from being ignored. Figure 10 shows the PP<br>instruction timing sequence.                                                                                                                                                                                                                                                   |  |  |

|                                                  | Continued on next page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

WWW.DATAKEY.COM

The power of memory. Secured.

Programming pages transmit 256 bytes in the same instruction. All data transmissions within the instruction will be programmed within the same page. If the beginning address transmitted with the PP instruction points to a location not at the beginning of a page (address bits A7 - A0 equal "0"), then the address pointer will roll over to the beginning of the current page if the address exceeds the page boundary. Similarly, if you transmit more than 256 bytes of data with the PP instruction, the current data will be overwritten before programming the page.

Continued on next page

| Self-timed page<br>programming<br>cycle | The self-timed page programming cycle begins when the /CS signal is driven high.<br>The page programming cycle time specifies the maximum duration of the page<br>programming cycle. During this cycle, you can read the status register with the read<br>Status Register (RDSR) instruction to monitor the write-in-progress (WIP) bit. The<br>WIP bit will have a value of "1" during a programming cycle. After completing the<br>programming cycle, the WIP bit and the write-enable-latch (WEL) bit will be set to<br>"0." A Page Program instruction will have no effect on pages within a protected<br>block. |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Sector Erase<br>(SE) instruction        | The Sector Erase instruction sets all bits within the addressed sector to a value of "1."<br>Use the SE instruction to erase the memory locations within a sector (FFh) before<br>writing data. To be effective, precede the SE instruction with a Write Enable<br>instruction.                                                                                                                                                                                                                                                                                                                                      |  |  |

| SE instruction<br>timing                | Execute the SE instruction by selecting the device with a low level on the /CS signal—transmitting the instruction on the SI signal, followed by a 24-bit address that addresses a location within the sector. The self-timed erase cycle begins when the /CS signal is driven high after clocking in the last bit of the last address byte.<br>Figure 11 shows the SE instruction timing sequence. Table 4 on page 13 shows the range of addresses within sectors for all memory device sizes.<br>/SC                                                                                                               |  |  |

Figure 11: SE Instruction Timing Sequence

Continued on next page

| Sector erase<br>cycle duration                                                                                                                                                                                                                                                                                                                                                                                               | The maximum duration of the sector erase cycle is specified by $t_{SE}$ . During this cycle, you can read the status register with the Read Status Register (RDSR) instruction to monitor the WIP bit. The WIP bit will have a value of "1" during an erase cycle. After completing the erase cycle, the WIP bit and the WEL bit will be set to "0." The SE instruction will have no effect on sectors within protected blocks. |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Chip or Bulk<br>Erase (CE)<br>Instruction The Chip Erase instruction sets all bits in the entire memory to a value of "1."<br>effective, precede the CE instruction with a Write Enable instruction. Execut<br>instruction by selecting the device with a low level on the /CS signal—transm<br>the instruction on the SI signal and deselecting the device. Figure 12 shows t<br>or Bulk Erase instruction timing sequence. |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | scк 0 1 2 3 4 5 6 7<br>scк Instruction<br>si (                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 12: CE Instruction Timing Sequence                                                                                                                                                                                                                                                                                                                                                                                       |  |

**Chip or bulk** erase cycle duration The maximum duration of the chip or bulk erase cycle is specified by t<sub>BE</sub>. This value depends on the size of the memory device. During the chip erase cycle, you can read the status register with the RDSR instruction to monitor the WIP bit. The WIP bit will have a value of "1" during a programming cycle. After completing the programming cycle, the WIP bit and the WEL bit will be set to "0."

If one or more BP bits are set, the CE instruction will be ignored.

Continued on next page

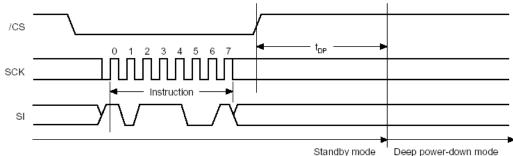

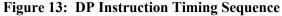

**Deep Power-**Down (DP) instruction

The DP instruction places the device in the lowest current consumption mode possible without fully removing the power. This mode can be used to further protect memory from inadvertent write or erase conditions since all instructions except a Release from DP/Read Electronic Signature (RES) instruction will be ignored. Execute the DP instruction by selecting the device with a low level on the /CS signal—transmitting the instruction on the SI signal, and deselecting the device. The /CS high to powerdown mode  $(t_{DP})$  determines when the device will enter deep power-down mode.

Figure 13 shows the DP instruction timing sequence.

**Deep power-**Cycling power to the device will cancel deep power-down mode. The memory device down mode always powers up in standby mode. The DP instruction will be ignored if transmitted cancellation during an erase or programming cycle.

Read Electronic In the deep power-down mode, the memory device will only recognize the Release Signature from DP/Read Electronic Signature (RES) instruction. The RES instruction will place (RES) the device in standby mode. You can also issue a RES instruction while the device is active to read the electronic signature of the device.

*Continued on next page*

**RES instruction** Execute the RES instruction by selecting the device with a low level on the /CS signal—transmitting the instruction and three dummy bytes on the SI signal. The single byte electronic signature of the device shifts out on the SO pin with the falling edge of the SCK, following the last bit of the third dummy byte. After reading the electronic signature at least once, you can terminate the RES instruction by deselecting the device with a high level on the /CS signal. Output of the electronic signature byte will be repeated as long as the device remains selected and an SCK signal is provided.

Figure 14 shows the RES instruction timing sequence.

Figure 14: RES Instruction Timing Sequence

**RES instruction** and memory size The electronic signature is unique for each memory device size. The RES instruction is a convenient method of determining the size of the memory device being selected. See Table 4 on page 13 for a list of electronic signature bytes based on memory size. If you transmit the RES instruction during a Programming or Erase instruction, the

If you transmit the RES instruction during a Programming or Erase instruction, the RES instruction will be ignored.

#### Panel- and board-mount receptacle descriptions

| Receptacles                          | The receptacles are used to interface the host system directly with specific serial data keys and tokens. The styles are the KC4210, KC4210PCB, SR4210, and the SR4210PCB.                                                                                                                                                                                                                                                                                            |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | A Last On/First Off (LOFO) switch in the key or token receptacle enables the host system to determine when a key or token is present. Upon insertion of a key or token, the LOFO contact connects to ground. Conversely, when the key is removed, the LOFO contact is open. The LOFO contact allows system designers to detect the presence of a key or token and protect the host bus by only applying power after the device has been fully inserted into the host. |

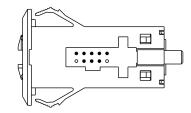

| KC4210 panel-<br>mount<br>receptacle | The KC4210 panel-mount version is designed for applications that require easy mounting in a front panel configuration. Figure 15 shows the panel-mount KC4210 receptacle.                                                                                                                                                                                                                                                                                             |

|                                      | To mount the device, simply cut a one-inch square hole in the desired panel location and snap the receptacle into place. Use a standard 10-pin connector cable ( $5 \times 2 \text{ pin}$ configuration) to connect the device to the host.                                                                                                                                                                                                                           |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Figure 15: Panel-Mount KC4210 receptacle

**Note:** Do not allow the total length of the signal conductors for PC board traces and ribbon cables to exceed eight inches.

Continued on next page

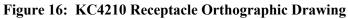

KC4210Figure 16 shows the KC4210 panel-mount receptacle. Refer to spec sheet for<br/>dimensions.drawingFigure 16 shows the KC4210 panel-mount receptacle. Refer to spec sheet for<br/>dimensions.

*Continued on next page*

**KC4210 pin** Figure 17 shows KC4210 receptacle pin outs.

| Pin No. | Description          |

|---------|----------------------|

| Pin 1   | NC                   |

| Pin 2   | Power (Vcc)          |

| Pin 3   | Ground (Vss)         |

| Pin 4   | /HOLD                |

| Pin 5   | Chip Select (/CS)    |

| Pin 6   | Serial Data In (SI)  |

| Pin 7   | Serial Clock (SCK)   |

| Pin 8   | Serial Data Out (SO) |

| Pin 9   | NC                   |

| Pin 10  | LOFO                 |

Receptacle Bottom View

Figure 17: KC4210 Receptacle Pin Outs

WWW.DATAKEY.COM

Continued on next page

**Datakey**

The power of memory. Secured.

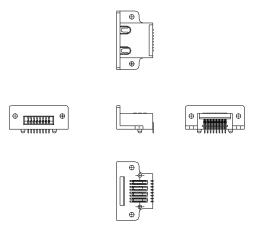

KC4210PCB board-mount receptacle The KC4210PCB board-mount receptacle is designed for applications where the designer wants to mount the device directly onto a printed circuit board (PCB). Figure 18 shows the KC4210PCB receptacle. In these applications, the receptacle connects to the host by soldering the leads onto a PCB.

#### Figure 18: KC4210PCB Board-Mount Receptacle

**KC4210PCB** Figure 19 shows the KC4210PCB receptacle. Refer to spec sheet for dimensions. **drawing**

| <u>- 10111101 -</u> | - 10 |

|---------------------|------|

Figure 19: KC4210PCB Receptacle Orthographic Drawing

WWW.DATAKEY.COM

29

30 Continued on next page

Panel- and board-mount receptacle descriptions, continued

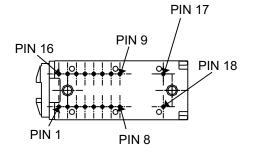

**KC4210PCB** Figure 20 shows KC4210PCB receptacle pin outs.

| Pin No. | Description               |

|---------|---------------------------|

| Pin 1   | /HOLD                     |

| Pin 2   | Ground (V <sub>SS</sub> ) |

| Pin 3   | Power (V <sub>CC</sub> )  |

| Pin 4   | NC                        |

| Pin 5   | Serial Data Out (SO)      |

| Pin 6   | Chip Select (/CS)         |

| Pin 7   | Serial Clock (SCK)        |

| Pin 8   | Serial Data In (SI)       |

| Pin 9   | Serial Data In (SI)       |

| Pin 10  | Serial Clock (SCK)        |

| Pin 11  | Chip Select (/CS)         |

| Pin 12  | Serial Data Out (SO)      |

| Pin 13  | NC                        |

| Pin 14  | Power (V <sub>CC</sub> )  |

| Pin 15  | Ground (V <sub>SS</sub> ) |

| Pin 16  | /HOLD                     |

| Pin 17  | LOFO                      |

| Pin 18  | LOFO                      |

Figure 20: KC4210PCB Receptacle Pin Outs

KC4210 keyThe KC4210 panel- and board-mount receptacles accept SFK and SFK5V keys. SeestyleFigure 21.

WWW.DATAKEY.COM

Figure 21: SFK and SFK5V Key

**Datakey** The power of memory. Secured.

## SPI Flash Interface Specification

31 Continued on next page

#### Panel- and board-mount receptacle descriptions, continued

SR4210 panelmount receptacle

The SR4210 panel-mount version is designed for applications that require easy mounting in a front-panel configuration. To mount the SR4210 panel-mount receptacle, simply cut a hole based on the dimensions shown on the SR4210 spec sheet in the desired panel location and then slip it into place. A standard 10-pin connector cable ( $5 \times 2$ ) is used to connect the device to the host. A Last On/First Off (LOFO) switch in the receptacle enables the host system to determine when a token is present. Figure 22 shows the SR4210 panel-mount receptacle.

#### Figure 22: SR4210 Panel-Mount Receptacle and Clip

**Note:** Do not allow the total length of the signal conductors for PC board traces and ribbon cables to exceed eight inches.

SR4210Figure 23 shows the SR4210 panel-mount receptacle. Refer to spec sheet for<br/>dimensions.orthographicdimensions.

|--|

| ſL. |         |   |

|-----|---------|---|

| ᄩ   |         | Ъ |

|     |         |   |

|     |         |   |

|     |         |   |

| IШ  | ه نضصاه | B |

| lþ  |         | ٣ |

| н   |         |   |

#### Figure 23: SR4210 Receptacle Orthographic Drawing

# SPI Flash Interface Specification

Continued on next page

#### Panel- and board-mount receptacle descriptions, continued

SR4210 pin Figure 24 shows SR4210 panel-mount receptacle pin outs.

Pin Description Pin 1 NC Power ( $\overline{V_{CC}}$ ) Pin 2 Pin 3 Ground (Vss) NC Pin 4 Chip Select (/CS) Pin 5 Pin 6 Serial Data In (SI) Serial Clock (SCK) Pin 7 Pin 8 Serial Data Out (SO) Pin 9 /HOLD Pin 10 LOFO

Figure 24: SR4210 Receptacle Pin Outs

Continued on next page

WWW.DATAKEY.COM

The power of memory. Secured.

.1

| SR42XXPCB<br>mount<br>receptacles      | board-mount receptacles. Dimensions can be found in the corresponding spec sheets.<br>Contact the factory for information on SMT options.                                                                                                                                                                       |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

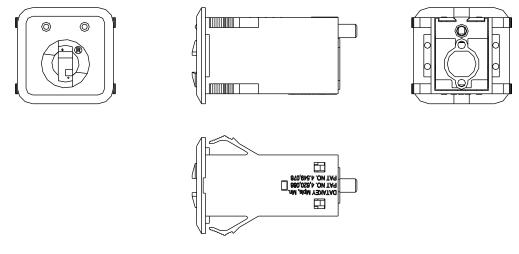

| SR4210PCB<br>board-mount<br>receptacle | The SR4210PCB board-mount receptacle is designed for applications where the designer wants to mount the device directly onto a printed circuit board (PCB). Figure 25 shows the SR4210PCB board-mount receptacle. In these applications, the receptacle connects to the host by soldering the leads onto a PCB. |

GD (010D GD 1 1

Figure 25: SR4210PCB Board-Mount Receptacle

SR4210PCB<br/>orthographicFigure 26 shows the SR4210PCB board-mount receptacle. Refer to spec sheet for<br/>dimensions.drawingFigure 26 shows the SR4210PCB board-mount receptacle. Refer to spec sheet for<br/>dimensions.

Figure 26: SR4210PCB Board-Mount Receptacle Orthographic Drawing

WWW.DATAKEY.COM

CD 4000 CD 4000

. 1

Continued on next page

Panel- and board-mount receptacle descriptions, continued

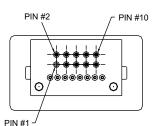

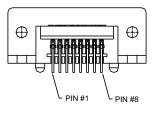

**SR4210PCB** Figure 27 shows SR4210PCB receptacle pin outs. pin outs

| Pin   | Description          |

|-------|----------------------|

| Pin 1 | /HOLD                |

| Pin 2 | Power (Vcc)          |

| Pin 3 | Chip Select (/CS)    |

| Pin 4 | Serial Clock (SCK)   |

| Pin 5 | Serial Data In (SI)  |

| Pin 6 | Serial Data Out (SO) |

| Pin 7 | Ground (Vss)         |

| Pin 8 | LOFO                 |

Figure 27: SR4210PCB Pin Outs

**Slim Token** styles

The SR4210 panel- and PCB-mount receptacles accept the IST- and ISX-token style with memory sizes from 1Kb to 512Kb. Figure 28 shows the token styles.

Figure 28: SFT Token and SFX Extended Token Styles

WWW.DATAKEY.COM

34

## SPI Flash Interface Specification

#### **Electrical interface**

AC/DC electrical characteristics 5 thru 8 show specific common DC and AC electrical characteristics for SPI Flash keys and tokens. These devices are available with nominal supply voltages of 3.3 and 5.0 volts. Table 5 shows the absolute maximums for both versions of the keys and tokens. Table 6 shows the DC operating characteristics for the 3.3-volt version. Table 7 shows the DC operating characteristics for the 5.0-volt version. Table 8 shows the AC characteristics for the devices.

# Maximum<br/>specificationsStressing SPI Flash keys and tokens beyond the limits specified in Table 5 could<br/>cause permanent damage to the device. The conditions are stress ratings only.<br/>Exposure to absolute maximum stress levels for extended periods could affect device<br/>reliability. Tables 6 thru 8 specify operating levels for the devices.

| Symbol              | Parameter                                  | Min/Max     | Units |

|---------------------|--------------------------------------------|-------------|-------|

| V <sub>CC</sub>     | Supply Voltage (3.3 volt versions)         | -0.6 to 4.0 | V     |

|                     | Supply Voltage (5.0 volt versions)         | -0.3 to 6.0 | V     |

| V <sub>IN/OUT</sub> | All pins w.r.t. Ground (3.3 volt versions) | -0.6 to 4.0 | V     |

|                     | All pins w.r.t. Ground (5.0 volt versions) | -0.3 to 6.0 | V     |

| T <sub>STG</sub>    | Storage temperature                        | -65 to 150  | °C    |

| T <sub>BIAS</sub>   | Operating temperature                      | -40 to 85   | °C    |

Table 5: Absolute Maximum Values and Temperature

Continued on next page

| Symbol           | Parameter                            | Min       | Max     | Units | Conditions                                           |

|------------------|--------------------------------------|-----------|---------|-------|------------------------------------------------------|

| V <sub>CC</sub>  | Supply voltage                       | 2.7       | 3.6     | V     | Conditions                                           |

| V <sub>IH</sub>  | High-level voltage input             | 0.: Vcc   | Vcc+0.4 | V     |                                                      |

| V <sub>IL</sub>  | Low-level voltage input              | -0.3      | 0.2Vcc  | V     |                                                      |

| Voh              | High-level voltage output            | Vcc - 0.2 |         | V     | $I_{OH} = -100 \ \mu A$                              |

| V <sub>OL</sub>  | Low-level voltage output             |           | 0.4     | V     | $I_{OL} = 1.6 \text{ mA}, I_{OL} = 100 \mu\text{A*}$ |

| $I_{LI}$         | Input leakage current                |           | $\pm 2$ | μA    |                                                      |

| I <sub>LO</sub>  | Output leakage current               |           | ± 2     | μA    |                                                      |

| I <sub>CC1</sub> | Standby current                      |           | 50.0    | μA    | $/CS = Vcc, VI_N = Vcc \text{ or } Vss$              |

| I <sub>CC2</sub> | Deep power-down current              |           | 5.0     |       | $/CS = Vcc, V_{IN} = Vcc \text{ or } Vss$            |

| I <sub>CC3</sub> | Operating current (read)             |           | 15.0    | mA    | SCK = 0.1Vcc to 0.9Vcc,<br>25MHz, SO = open          |

| I <sub>CC4</sub> | Operating current (page program)     |           | 25.0    | mA    | /CS = Vcc                                            |

| I <sub>CC5</sub> | Operating current (write status reg) |           | 25.0    | mA    | /CS = Vcc                                            |

| I <sub>CC6</sub> | Operating current (sector erase)     |           | 25.0    | mA    | /CS = Vcc                                            |

| I <sub>CC7</sub> | Operating current (chip erase)       |           | 25.0    | mA    | /CS = Vcc                                            |

| C <sub>OUT</sub> | Output capacitance                   |           | 8.0     | pF    | $V_{OUT} = 0$                                        |

| C <sub>IN</sub>  | Input capacitance                    |           | 6.0     | pF    | $V_{IN} = 0$                                         |

## Table 6: DC Characteristics for 3.3-Volt Keys and Tokens

\*For 8Mbit and 32Mbit devices only

Continued on next page

36

| Symbol                     | Parameter                               | Min       | Max  | Units | Conditions                                  |

|----------------------------|-----------------------------------------|-----------|------|-------|---------------------------------------------|

| $V_{CC}$                   | Supply voltage                          | 3.8       | 5.5  | V     |                                             |

| $\mathbf{V}_{\mathrm{IH}}$ | High level voltage input                | Vcc - 0.4 | Vcc  | V     |                                             |

| $V_{IL}$                   | Low level voltage input                 | 0.0       | 0.2  | V     |                                             |

| V <sub>OH</sub>            | High level voltage output               | 0.67Vcc   |      | V     | $I_{OH} = -100 \text{ uA}$                  |

| Vol                        | Low level voltage output                |           | 0.4  | V     | $I_{OL} = 1.6 \text{ mA}$                   |

| I <sub>CC1</sub>           | Standby current                         |           | 1.0  | mA    | $/CS = Vcc, V_{IN} = Vcc \text{ or } Vss$   |

| I <sub>CC2</sub>           | Deep power-down current                 |           | 1.0  | mA    | $/CS = Vcc, V_{IN} = Vcc \text{ or } Vss$   |

| I <sub>CC3</sub>           | Operating current (read)                |           | 16.0 | mA    | SCK = 0.1Vcc to 0.9Vcc,<br>25MHz, SO = open |

| I <sub>CC4</sub>           | Operating current (page program)        |           | 21.0 | mA    | /CS = Vcc                                   |

| I <sub>CC5</sub>           | Operating current (write status reg)    |           | 21.0 | mA    | /CS = Vcc                                   |

| I <sub>CC6</sub>           | Operating current (sector erase)        |           | 26.0 | mA    | /CS = Vcc                                   |

| I <sub>CC7</sub>           | Operating current ( <i>chip erase</i> ) |           | 26.0 | mA    | /CS = Vcc                                   |

| Table 7:   | DC Electrical | Characteristics  | for 5.0-Vol | t Keys and Tokens    |

|------------|---------------|------------------|-------------|----------------------|

| I abit / . |               | Character istics | 101 0.0 101 | t ixtys and i onthis |

Continued on next page

37

|                   | Table 6. AC Characteristics                         |      |     |       |                  |

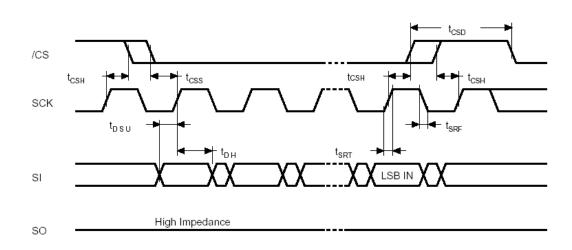

|-------------------|-----------------------------------------------------|------|-----|-------|------------------|